# Verification of SoC using Advanced Verification Methodology

## Pranuti Pamula, Durga Prasad Gorthy, Phalguni Singh Ngangbam and Aravindhan Alagarsamy\*

Multi-Core Architecture Computation (MAC) Lab, Department of ECE, Koneru Lakshmaiah Education Foundation, Andhra Pradesh, 522501 AMD, Hyderabad, 500081

### **INTRODUCTION**

- $\checkmark$  In the past few decades, there has been tremendous progress in semiconductor industry from printed circuit boards to a multi-million gate design i.e., a System on Chip.

- ✓ SoC provides faster and reliable implementation design with low cost per gate and considerably low power consumption.

- $\checkmark$  In addition to this, it also offers a smaller physical size and with greater design security.

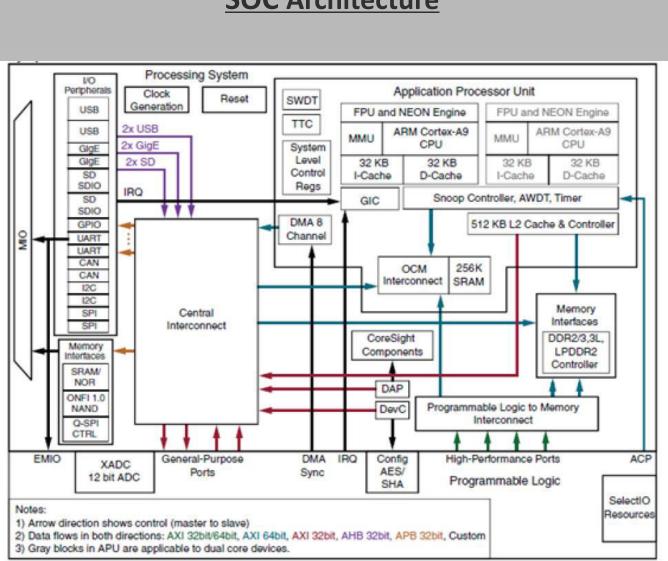

- $\checkmark$  The functional verification of the design is done by using system verilog and UVM testbench which includes creation of testcases, assertions and checkers for verifying different functionality as per the design specifications.

- $\checkmark$  A unique functional block which is present on the interconnect to slave interface is verified by using combination of checkers and test sequences.

- Trace monitoring of the transactions on AXI interface of the interconnect is done by programming different operational pointers and filters.

### **Challenges in verification**

With devices getting smarter day by day, the complexity of operation shave gone up. Interaction points with users have increased. Some IoT based smart devices now continuously collect and process information.

- Reduction in available verification time

- Wrongly capturing specifications

- Usage scenarios for Devices

- Power consumption of devices

- Security

- Co-verification of hardware and software

- Analogue -digital amalgamation

### Latest Trends in verification

- Simulation

- Mixed signal verification

- Verification and Power dependencies

- Data Analytics

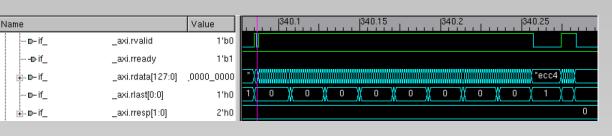

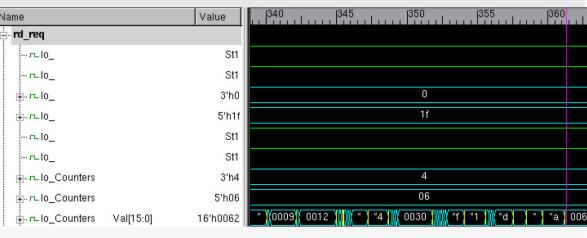

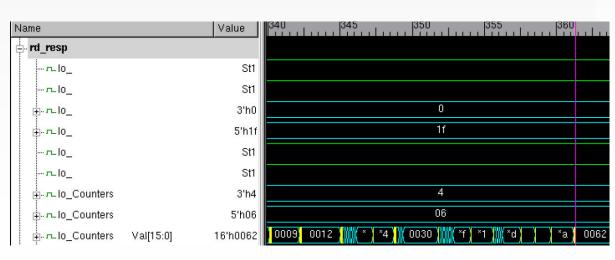

### Figure 3: Read operation of AXI Burst Transfer

| Name                | Value     |          |

|---------------------|-----------|----------|

| <sup>⊨</sup> wr_req |           |          |

|                     |           | St1      |

|                     |           | St1      |

| <u>⊕</u>            |           | 3'h0     |

| <u>⊨</u>            |           | 5'h1f    |

|                     |           | St1      |

|                     |           | St1      |

| ⊕ Io_Counters       |           | 3'h4     |

| ⊷ ہے۔ Io_Counters   |           | 5'h06    |

| ∯∝ - Lo_Counters    | Val[15:0] | 16'h0062 |

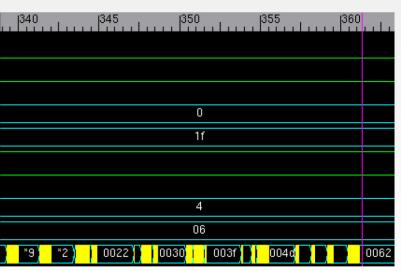

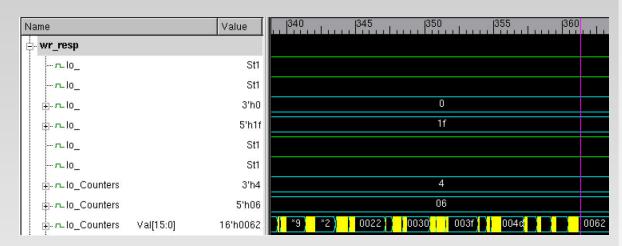

Figure 7: Write Response Transfers

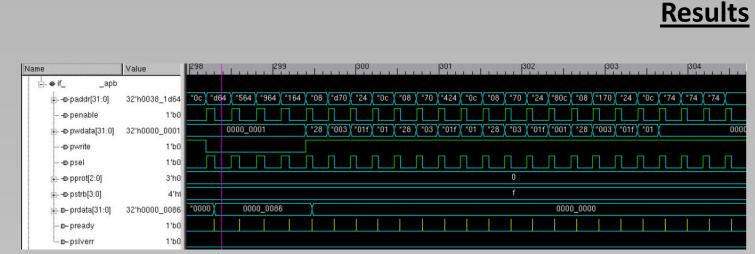

### Figure 1: Configuration of Pointers

| 340.068    |            | .07        | 340.072    | 340        | ).074      | 340.076 |  |

|------------|------------|------------|------------|------------|------------|---------|--|

|            |            |            |            |            |            |         |  |

|            |            |            |            |            |            |         |  |

| ʻfffc_0100 | *fffc_0200 | *fffc_0300 | *fffc_0400 | *fffc_0500 | *fffc_0600 |         |  |

|            |            |            |            |            |            |         |  |

| 344 , , , , , , , , , , , , , , , , , ,         |                            |                                              |

|-------------------------------------------------|----------------------------|----------------------------------------------|

|                                                 |                            |                                              |

|                                                 |                            |                                              |

| 10_ffc_0508 /////////////////////////////////// | 80 <u> </u>                | 0_fffc_0998                                  |

|                                                 |                            |                                              |

| _05b7_7cf8 \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ | )4fc                       | b65_bc5c ))))))))))))))))))))))))))))))))))) |

| 1 1111111111111111111111111111111111111         |                            | 1                                            |

|                                                 |                            |                                              |

|                                                 |                            |                                              |

| 0                                               |                            |                                              |

|                                                 |                            |                                              |

|                                                 |                            |                                              |

| xxxx_x000_fffc_0508 ))))()()))()()()()(x0_fffc_ | _0980 *000_ffc_0390 / //// | xxx_x000_ffc_0998 ()()()()()()()(000.        |

|                                                 |                            |                                              |

|                                                 |                            |                                              |

| "C9C1_cf6Z_33bd_05b7_7cf6                       | _04fc) *0_dd85_26c9        | 91_c0ad_f757_zb65_bc5c                       |

| 1 10010000 1                                    |                            | 1                                            |

| 0                                               |                            |                                              |

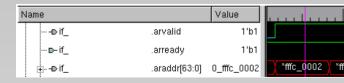

### Figure 5: Burst Traffic on AXI Interface

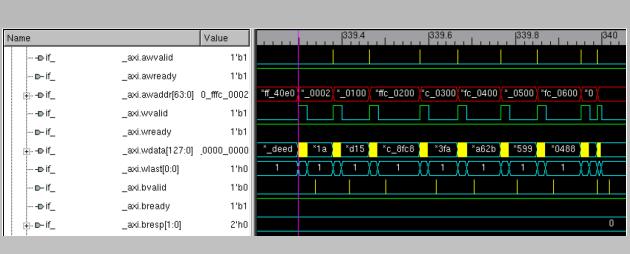

### Figure 2: Write operation of AXI Burst Transfer

### Figure 4: Read Response on AXI Burst Transfer

### Figure 6: Write Request Transfers

### Figure 9: Read Request Transfers

### Figure 9: Read Response Transfers

- P. Ghosh and R. Srivastava, "Case Study: SoC Performance Verification and Static Verification of RTL Parameters," IEEE Proc 20th International Workshop on Microprocessor/SoC Test, Security and Verification (MTV), pp. 65–72, 2019.

- Noguera, Juanjo, and Rosa M. Badia. "System-level powerperformance trade-offs in task scheduling for dynamically reconfigurable architectures." Proceedings of the 2003 international conference on Compilers, architecture and synthesis for embedded systems. 2003

- Spear, Chris. SystemVerilog for verification: a guide to learning the testbench language features. Springer Science & Business Media, 2008.

### **SOC** Architecture

### REFERENCES

- Najm, Farid, and Jay Abraham. "Accounting for very deep sub-micron effects in silicon models." *EEdesign* Magazine (2001).

- Tuomi, Ilkka. "The lives and death of Moore's Law." First Monday (2002).

- Xilinx (2017), 'Zynq-7000 all programmable soc data.