# The 4th International Online Conference on Materials

03-05 November 2025 | Online

## Capacitive Behavior of Poly-Si Thin Films in TFTs: Optimizing Device Performance through 2D Numerical Modeling

Hadjira Tayoub<sup>1,2</sup>, Ahlam Harhouz<sup>2</sup>, Farida Kebaili<sup>2</sup>

<sup>1</sup>Research Center in Industrial Technologies, CRTI, P.O. Box 64, Cheraga, 16014 Algiers, Algeria <sup>2</sup>Laboratoire d'Analyse des Signaux et Systèmes, Department of Electronics, University of M'Sila BP.166, Route Ichebilia, M'Sila, 28000, Algeria

### INTRODUCTION & AIM

- •Low-Temperature Polycrystalline-Silicon (LTPS) TFTs are crucial for microelectronics, optoelectronics, and large-area displays (like active-matrix organic light-emitting diode displays) due to their high carrier mobility.

- •However, LTPS films contain a high density of defects, particularly grain boundaries (GBs), which trap carriers, reduce mobility, and impact device characteristics like capacitance-voltage C(V) curves.

- •Previous work addressed the quasi-static capacitance, but the high-frequency C-V behavior needed further investigation.

- •AIM: To develop a 2D numerical simulation code to understand the high-frequency capacitance behavior of the Al/SiO<sub>2</sub>/poly-Si structure as a function of the granular structure (number of grain boundaries, grain size, and layer thickness) and oxide thickness.

#### **METHOD**

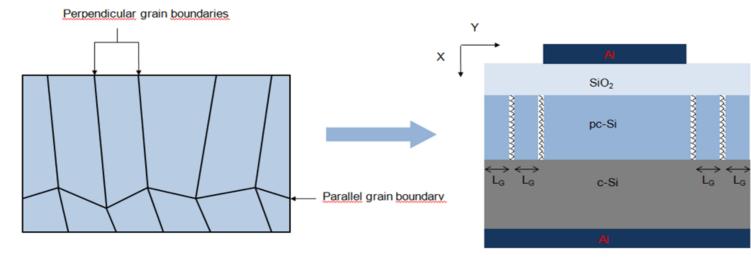

#### **Studied Structure:**

- •The polysilicon film is modeled with a columnar structure.

- •It is composed of identical single-crystal grains (L<sub>G</sub>=200 nm) separated by grain boundaries (GBs), which are highly defective regions.

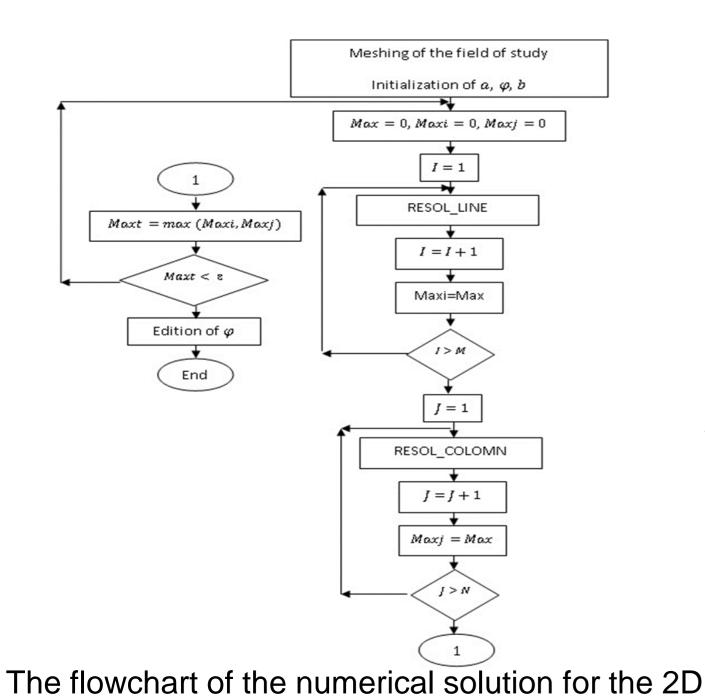

The 2D schematic cross-sectional structure of the Al/SiO<sub>2</sub>/poly-Si system •A custom 2D numerical simulation code was developed based on the solution of the Poisson's equation:

$$div\left(\varepsilon \overrightarrow{grad} \varphi\right) = -q \left(p - n - N_A^- + N_D^+ + \sum N_T\right)$$

•The high-frequency capacitance  $C(V_G)$  is calculated from the following relation:

$$C = \frac{dQ_m}{dV_G}$$

•The simulation determines the behavior of the active layer by applying a transverse gate voltage (V<sub>G</sub>) across the SiO<sub>2</sub> layer.

Poisson equation

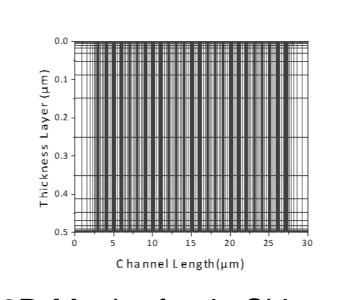

2D-Mesh of poly-Si layer

#### **RESULTS & DISCUSSION**

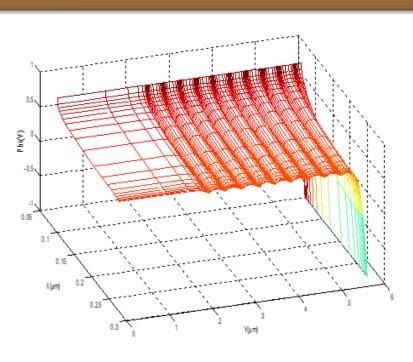

#### I. Layer at Thermodynamic Equilibrium

The localized density of states in the GBs traps free carriers, creating a height potential barrier surrounding the grain boundaries when the crystallites are depleted.

### **II. Impact of Granular Structure and Oxide Thickness**

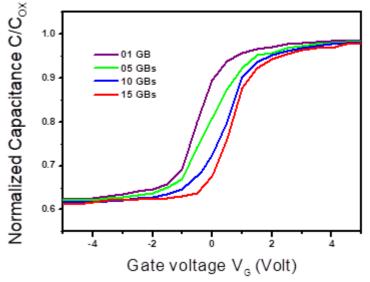

- •Impact of Number of Grain Boundaries  $(N_{\text{GB}})$

- ✓ An increase in  $N_{GB}$  increases  $V_{T}$  of the high-frequency capacitance.

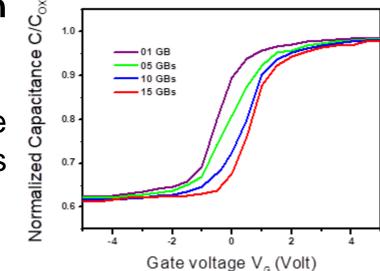

- Impact of Layer Thickness (L<sub>C</sub>) and Grain Size (L<sub>G</sub>)

- ✓ Increasing L<sub>C</sub> and L<sub>G</sub> leads to an increase in V<sub>T</sub>

- Discussion: The increase in VT is due to the presence of GBs, which act as potential barriers and restrict the flow of charge carriers.

- Impact of Oxide Thickness (d<sub>OX</sub>)

- ✓ The increasing of the granular structure increases V<sub>T</sub>.

- ✓ the presence of GBs in the channel are primarily responsible for the scattering of majority carriers.

- ✓ It creates a potential barrier that restricts the flow of charge carriers from grain to grain

## CONCLUSION

- •The study demonstrated that the capacitive effect of poly-Si layers is strongly related to their granular structure ( $N_{GB}$ ,  $L_{G}$ , and  $L_{C}$ ).

- •The threshold voltage  $(V_T)$  is very sensitive to the number of grain boundaries and also depends on the layer thickness and grain size.

- •To achieve the best performance for poly-Si TFT active layers, the solution is to:

- ✓ Increase the grain size (implying fewer grain boundaries).

- Reduce the Density of States (DOS) content at the grain boundaries.

#### REFERENCES

- [1] Sze, S.M.: Physics of Semiconductor Devices.

- [2] Fortunato, E. et al.: Recent advances in ZnO transparent thin film transistors.

- [3] Seto, J. Y. W.: The electrical properties of polycrystalline silicon films.

- [4]Tayoub, H. et al.: 2D Numerical Analysis of Metal/Insulator/Thin Film Silicon Systems for TFT's Applications.

- [5] Lu, C. Y. et al.: The effect of film thickness on the electrical properties of LPCVD polysilicon films.